Bare Machine - NAND

by 宋强

Nand Flash中的存储结构是一种类似于场效应管的存储结构,向浮动栅极注入电压进行存储,每一个这样的存储结构成为一个存储单元,可以存储1bit的数据,8bit或者16bit的存储单元可以构成一个Line,多个Line会组成页(Page),多个Page又会组成块(Block)。

我所见的几个Nand Flash,数据总线都是8位的,还不能够确定所有的Nand Flash都是这样的,对于Nand Flash来说,数据和地址都是通过这八条线传输的,只不过存在一个时序问题。

通常在组成页的时候,页的内容会被分为两部分,一部分是主内存(Main Memory),也就是用来存储数据的部分,另一部分叫做空闲内存(Spare Memory),用来存储ECC、损耗均衡(Wear Leveling)等功能的实现。

在Nand Flash中,读和写的基本单位都是页(页定位,无法像RAM和NOR Flash一样进行字节定位),修改其中的很少的数据也要把整个页读取出来改了之后写进去。这个功能对于分页管理机制的代码来说是非常合适的,通常分页管理系统对于内存的读写单位恰恰也就是页。

擦除操作的基本单位是Block,无法Page擦除。

由于上述特点,Nand Flash在定位一个Byte的数据的时候就要存在三个地址:

- 块地址

- 页地址

- 页内偏移量

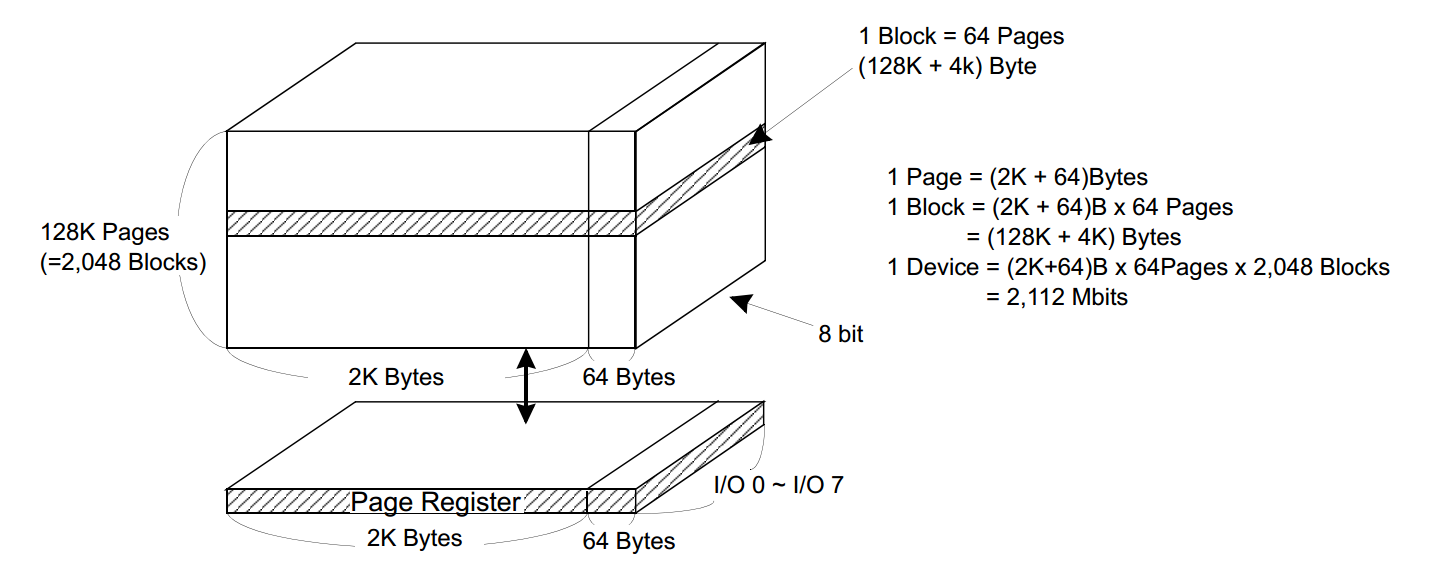

下面是三星公司的K9F2G8U0A的存储结构:

一个Nand Flash存储器内部的结构,摘自K9F2G08U0A datasheet。

从上面图可以看出,这个芯片包含了2048个块,每一个快包含64页,每一页包含2K+64的字节,2K是主内存,64是空闲内存。因为这个芯片是32位的,所以Line的话就是32bit构成的。

向Nand发送地址和命令,是通过控制ALE和CLE上,写命令的时候CLE失能,写地址的时候ALE失能来完成的,这一点和网络适配器很相似,现在觉得高速的通信设备可能都是这样完成的。

tags: NAND